- 1. O que é um conjunto de instruções?

- 2. Quais os principais elementos de uma instrução?

- 3. Quais são as questões mais importantes no projeto do conjunto de instruções? Explique cada uma delas.

- 4. Quais são as principais classes de operações executadas pelas instruções?

- 5. (Exercício 9.3 Stallings) Compare máquinas com instruções de um, dois e três endereços, escrevendo um programa, em cada uma dessas quatro máquinas, para implementar o comando:

$$X = (A + B + C) / (D - E * F)$$

As instruções disponíveis para as três máquinas são as seguintes:

| 1 endereço | 2 endereços                          | 3 endereços                             |

|------------|--------------------------------------|-----------------------------------------|

| LOAD M     | MOVE X, Y $(X \leftarrow Y)$         | MOVE X, Y $(X \leftarrow Y)$            |

| STORE M    | ADD X, Y $(X \leftarrow X + Y)$      | ADD X, Y, Z $(X \leftarrow Y + Z)$      |

| ADD M      | SUB X, Y $(X \leftarrow X - Y)$      | SUB X, Y, Z $(X \leftarrow Y - Z)$      |

|            | $MUL X, Y (X \leftarrow X \times Y)$ | $MUL X, Y, Z (X \leftarrow Y \times Z)$ |

| MUL M      |                                      | DIV X, Y, Z $(X \leftarrow Y/Z)$        |

| DIV M      | DIV X, Y $(X \leftarrow X/Y)$        |                                         |

- 6. Cite e explique os possíveis modos de endereçamento em uma arquitetura.

- 7. Quais são os principais fatores que afetam ou são afetados pelo formato da instrução?

- 8. Explique quais as diferenças entre o conjunto de instruções do MIPS e IA32.

- 9. (Exercício 10.1 Stallings) Justifique a afirmação de que uma instrução de 32 bits não é duas vezes mais útil que uma instrução de 16 bits.

- 10. (Exercício 10.2 Stallings) Dados os seguintes valores, armazenados na memória de uma máquina com instruções de um único endereço e com um acumulador, que valores são carregados no acumulador pelas seguintes instruções?

- Palavra 20 contém o valor 40

- Palavra 30 contém o valor 50

- Palayra 40 contém o valor 60.

- Palavra 50 contém o valor 70

- a) Carrega imediato 20

- b) Carrega direto 20

- c) Carrega indireto 20

- d) Carrega imediato 30

- e) Carrega direto 30

- f) Carrega indireto 30

- 11. (Exercício 10.5 Stallings) Quantas vezes a CPU acessa a memória quando busca e executa uma instrução com modo de endereçamento indireto, se a instrução é:

- a) Uma computação que requer um único operando

- b) Um desvio

- 12. Projete um código de operação com tamanho variável, de modo que permita que todas as operações a seguir sejam codificadas em uma instrução de 36 bits:

- a) 7 Instruções com dois endereços de 15 bits e um número de registrador de 3 bits;

- b) 500 Instruções com um endereço de 15 bits e um número de registrador de 3 bits;

- c) 40 Instruções sem endereços ou registradores

- 13. Quais são as principais ações executadas por uma CPU?

- 14. Qual a função dos registradores visíveis para o usuário e os registradores de controle e estado? Cite um exemplo de uso para cada um dos tipos.

- 15. Explique o diagrama de transição de estados da figura 11.6 (Stallings).

- 16. Explique detalhadamente (usando MAR, PC, MBR e IR) os ciclos de busca e indireto.

- 17. O que é um pipeline de instruções?

- 18. No que consiste a busca antecipada (ou prefetch)?

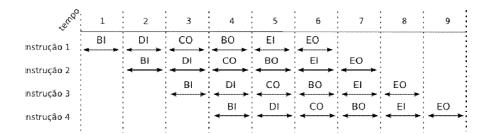

- 19. Considere o diagrama da Figura abaixo. Suponha que existe apenas uma pipeline de dois estágios (busca e execução). Redesenhe o diagrama e mostre quantas unidades de tempo são agora necessárias para quatro instruções.

Legenda:

BI – busca de instrução

DI – decodificação de instrução

CO – cálculo de operando

BO – busca de operando

EI – execução

EO – escrita de Operando

- 20. Um dos problemas do uso de pipeline é a execução de desvios.

- a) Explique o problema do pipeline da Figura 11.12 (Stallings).

- b) Quais são as formas de contornar este problema?

- 21. Em relação às arquiteturas CISC e RISC:

- a) Explique o surgimento destes tipos de arquiteturas dado seu contexto histórico;

- Represente em uma tabela as principais diferenças entre os dois tipos (O capítulo 12 do Stallings também pode ser consultado).

## Questões de Concurso

(CESPE - SEBRAEAC 2007) Para acelerar a execução, os processadores usam a técnica de pipelining de instruções, que consiste em dividir o ciclo de instrução em determinado número de estágios consecutivos, tal que cada estágio possa estar trabalhando em uma instrução diferente ao mesmo tempo. A ocorrência de desvios e de dependências entre instruções é um facilitador na utilização do pipelining. Um computador superescalar é aquele no qual são usadas várias pipelines de instruções. A afirmativa é verdadeira ou falsa? Justifique

(Poscomp/04) Ao segmentar um processador, transformando-o num pipeline, obtém-se:

- a) redução no número de ciclos necessários para executar uma instrução

- b) redução no número de ciclos necessários para executar um programa

- c) redução no número de ciclos necessários para tratar uma exceção

- d) redução no número de ciclos necessários para tratar uma interrupção

- e) o circuito do processador fica mais simples

A técnica de Pipeline melhora o desempenho dos processadores,

- a) reduzindo o tempo de execução de cada instrução individualmente.

- b) aumentando a vazão de instruções executadas na unidade de tempo.

- c) compactando as instruções executadas.

- d) diminuindo o tempo de acesso às memórias cache.

(Poscomp – 2008) Um processador tem cinco estágios de pipeline. Suponha que cada uma das etapas do processador (busca, decodificação, execução, leitura ou escrita de dados em memória e escrita em registrador) seja executada em 5ns. O tempo total para que 5 instruções sejam executadas em pipeline, supondo que não haja dependência de dados entre as instruções é:

- a) 15ns

- b) 25ns

- c) 30ns

- d) 45ns

- e) 50ns

(Poscomp – 2008) Assuma que um programa tem um profile de execução onde 85% das instruções são simples (tais como AND, XOR, ADD e BRANCH) e os 15% restantes são instruções complexas (tais como MUL e DIV). Adicionalmente, considere que as instruções simples precisam de 2 ciclos de máquina e as complexas precisam de 12 ciclos em uma máquina CISC (cada ciclo = 10 ns). Em uma máquina RISC, as instruções simples serão executadas em 1 ciclo, enquanto que as instruções complexas deverão ser simuladas por software necessitando, em média, 20 ciclos por instruções. Devido a sua simplicidade, o tempo de ciclo em uma máquina RISC é de 8 ns. Considere também que o programa precisou de 100.000.000 instruções para ser completado. Qual o tempo gasto em segundos na execução desse programa, respectivamente, nas máquinas CISC e RISC?

- a) 1 e 0,8

- b) 3,5 e 3,08

- c) 10 e 12,8

- d) 8,5 e 1,5

- e) 14 e 16,8